参考:

这个专栏还有覆盖率的介绍,可以看看

Icer_Newer博客园 PS: 也有许多验证的知识分享,虽然大部分知识点重合。

VCS编译选项,网上很多,随便贴几个吧,如下:

一、工作过程

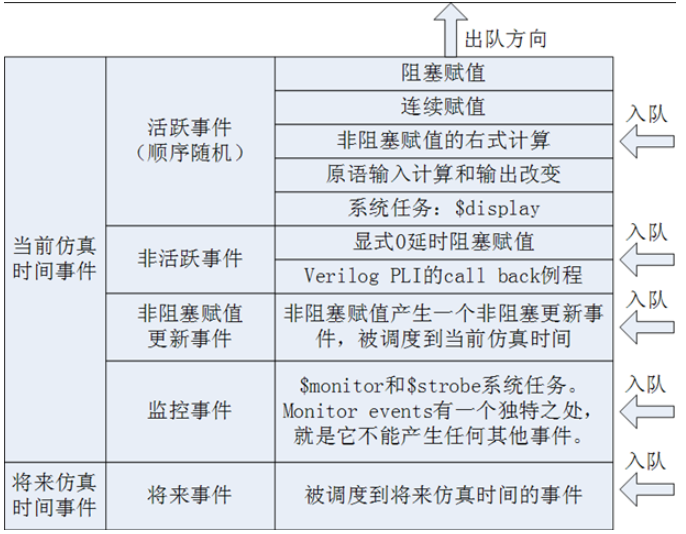

- 读取所有的 initial、always 、assgin 等语句,按照空间顺序放在队列里面。首先执行没有延时的语句(如变量的初始化赋值等)

- 执行完没有延时的语句之后,将时间 t 设为 0,称之为 current time。

- 然后,首先进入 active region。

在该区域内,VCS执行的操作包括:

① 原语(或门、非门、CMOS逻辑、PMOS逻辑、上拉、下拉 …);

② $display;

③ 不包含任何延时信息的 assgin 语句;

④ 阻塞赋值( = );

⑤ 非阻塞赋值( <= )只计算右边的表达式,不进行赋值操作 - 进入 inactive region

执行带有 #0 的语句。

虽然没有延时,但是对于VCS而言,这种语句会比没有使用 # 设置延时的语句的执行时间晚一些。 - 进入 Nonblocking assgin region

对非阻塞赋值语句进行赋值操作 - monitor region

monitor 系统函数是只有在变量发生变化的时候才会执行。 - future region

执行其他语句

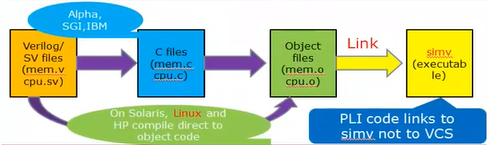

(1)将 Verilog/SV 翻译为 C 语言中间文件

(2)将 C 语言文件编译为对象文件(.o)

(3)连接后形成可执行文件

举例说明:

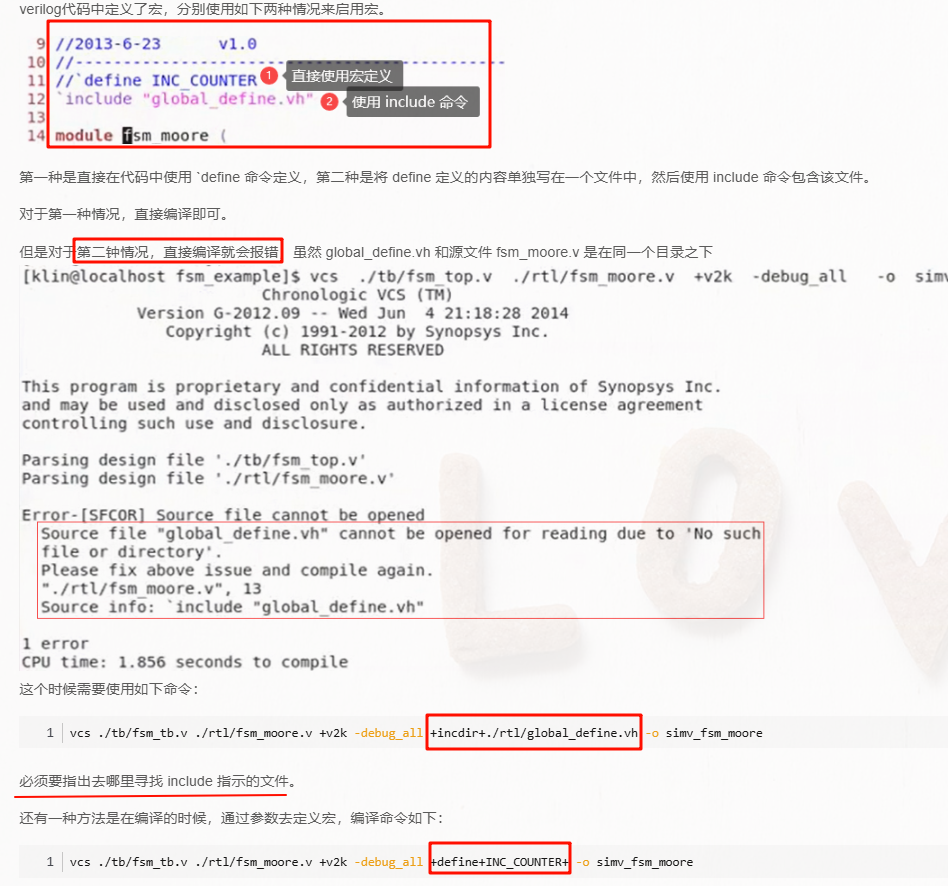

针对宏的编译:

转载请注明来源,欢迎对文章中的引用来源进行考证,欢迎指出任何有错误或不够清晰的表达。